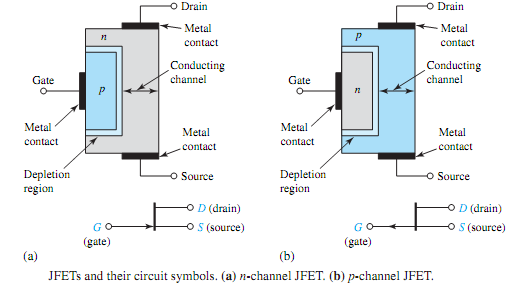

Q. Show Operation on JFET?

The junction in the JFETis reverse-biased for normal operation.No gate current flows because of the reverse bias and all carriers flow from source to drain. The corresponding drain current is dependent on the resistance of the channel and the drain-to-source voltage vDS.As vDS is increased for a given value of vGS, the junction is more heavily reverse-biased, when the depletion region extends further into the conducting channel. Increasing vDS will ultimately block or pinch off the conducting channel. After the pinch-off, the drain current iD will be constant, independent of vDS.

It is the active region beyond pinch-off that is useful for the controlled-source operation, since only changes in vGS will produce changes in iD. Figure illustrates the JFET characteristics. Part (a) shows the idealized static characteristics with two regions separated by the dashed line, indicating the ohmic (controlled-resistance or triode) region and the active (controlled-source) region beyond pinch-off. Note that iD is initially proportional to vDS in the ohmic region where the JFET behaves much like a voltage-variable resistance; iD depends on vGS for a given value of vDS in the active region. In a practical JFET, however, the curves of iD versus vDS are not entirely flat in the active region but tend to increase slightly with vDS, as shown in Figure(b);

when extended, these curves tend to intersect at a point of -VA on the vDS axis. Another useful characteristic indicating the strength of the controlled source is the transfer characteristic, relating the drain current iD to the degree of the negative bias vGS applied between gate and source; a cutoff region exists, indicated by the pinch-off voltage -VP , for which no drain current flows, because both vGS and vDS act to eliminate the conducting channel completely.

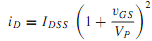

Mathematically, the drain current in the active controlled-source region is approximately given by:

where IDSS, known as the drain-source saturation current, represents the value of iD when vGS = 0.