Q. D flip-flop - latch or delay element?

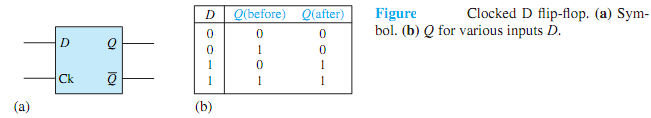

The symbol for the clocked D flip-flop is shown in Figure (a), in which the two output terminals Q and ¯ Q behave just as in the SRFF, and the input terminals are D and Ck (clock). The term clocked flip-flop indicates that this device cannot change its state (i.e., Q cannot change) unless a specific change instruction is given through the clock (Ck) input. The value of Q after the change instruction is equal to the value of D at the time the change instruction is received. The value of Q before the change instruction does not matter. Figure 6.1.20(b) illustrates the values taken by Q after the change instruction for various inputs D and prior values of Q. While there are several variations of the device, in the rising-edge triggered flip-flop a change instruction is effected whenever the Ck input makes a change from 0 to 1. Note that only a positive-going transition of Ck is a change instruction, and a constant Ck input is not a change instruction.

Note that flip-flops have propagation delay, whichmeans that there is a small delay (about 20 ns) between the change instruction and the time Q actually changes. The value of D that matters is its value when the change instruction is received, not its value at the later time when Q changes.

A convenient means of describing the series of transitions that occur as the signals set to the flip-flop input change is the timing diagram. A timing diagram depicts inputs and outputs (as a function of time) of the flip-flop (or any other logic device) showing the transitions that occur over time. The timing diagram thus provides a convenient visual representation of the evolution of the state of the flip-flop. However, the transitions can also be represented in tabular form.

Like logic blocks, flip-flops appear almost exclusively in IC form, and are more likely to be found in LSI and VLSI form. A very important application is in computer memories, in which a typical 256k RAM (random access memory) consists of about 256,000 flip-flops in a single IC.