Q. What is Enhancement MOSFETS?

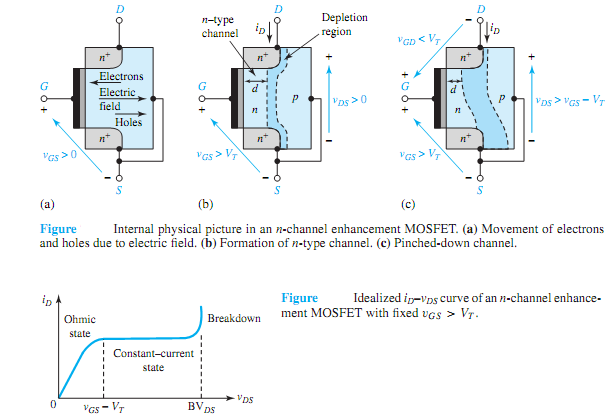

Figure illustrates the cross-sectional structure of an n-channel enhancement MOSFET and its symbol showing as a normally off device when used for switching purposes. When the gate-to-source voltage vGS > 0, an electric field is established pushing holes in the substrate away from the gate and drawing mobile electrons toward it, as shown in Figure (a). When vGS exceeds the threshold voltage VT of the MOSFET, an n-type channel is formed along the gate and a depletion region separates the channel from the rest of the substrate, as shown in Figure (b).With vGS > VT and vDS > 0, electrons are injected into the channel from the heavily doped n+ source region and collected at the n+ drain region, thereby forming drain-to-source current iD, as shown in Figure (b). Note that none of the electrons comes from the p-type portion of the substrate, which now forms a reverse-biased junction with the n-type channel. As the gate voltage increases above VT, the electric field increases the channel depth and enhances conduction. For a fixed vGS and small vDS, the channel has uniform depth d, acting like a resistance connected between the drain and source terminals. The MOSFET is then said to be operating in the ohmic state.

With a fixed vGS >VT , increasing vDS will reduce the gate-to-drain voltage vGD(= vGS - vDS), thereby reducing the field strength and channel depth at the drain end of the substrate.When vDS >(vGS - VT ), i.e., vGD < VT ,a pinched-down condition occurs when the electron flow is limited due to the narrowed neck of the channel, as shown in Figure(c). The MOSFET is then said to be operating in a constant-current state, when iD is essentially constant, independent of vDS.

Figure illustrates the MOSFET behavior explained so far. When vGS ≤ VT , however, the field is insufficient to form a channel so that the iD-vDS curve for the normally off state is simply a horizontal line at iD = 0. The drain breakdown voltage BVDS ranges between 20 and 50 V, at which the drain current abruptly increases and may damage the MOSFET due to heat if operation is continued. The gate breakdown voltage, at about 50 V, may also cause a sudden and permanent rupture of the oxide layer.