Instruction Formats

A machine language instruction format has 1 or more number of fields linked with it. The first field is known as operation code field or op code field, which show the type of the operation to be performed by the CPU. The instruction format also has other fields known as operand fields. The CPU executes the instruction by using the information which reside in these fields.

There are 6 general formats of instructions in 8086 instruction set. The length of an instruction can vary from one byte to six bytes. The instruction formats are given as following:

1) One byte Instruction: This format is just one byte long and can have theregister operands or implied data . The least significant 3-bits of the op code are referring for specifying the register operand, if any. Or else all the 8-bits form an opcode and the operands are implied.

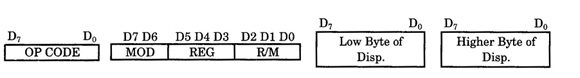

2) Register to Register: This format is 2 bytes long. The first byte of the code indicatethe operation code and width of the operand indicated by w bit. The second byte of the code indicate the register operands and R/M field, as given below.

The register represented by the REG field is 1 of the operands. The R/M field indicate another register or memory location, for example. the other operand.

3) Register to/from Memory with no Displacement: This format is 2 bytes long and same as the register to register format except for the MOD field as shown.

The MOD field indicates the mode of addressing. The R/M, MOD,REG and the W fields are decided inTable 3.2.

4) Register to/from Memory with Displacement: This type of instruction format have one or two extra bytes for displacement along with 2-byte the format of the register to/from memory without displacement. The format is given.

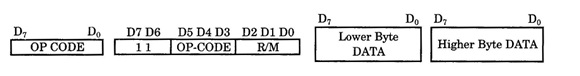

5) Immediate Operand to Register: In this format, the first byte and the 3-bits from the second byte which are utilized for REG field in case of register to register format are utilized for opcode. It also has one or two bytes of immediate data. The complete instruction format is as given below.

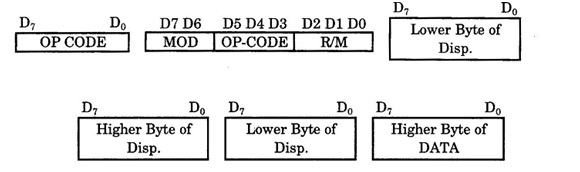

6) Immediate Operand to Memory with 16-bit Displacement: This type of instruction format requires 5 or 6 bytes for coding. The first 2 bytes have the information regardingMOD, OPCODE and R/M fields. The remaining 4 bytes have 2 bytes of displacement and 2 bytes of data as shown.