Q. In order to minimize output voltage offsets in practical op-amp circuits, one provides a dc path from each input terminal to ground, makes each input terminal see the same external resistance to ground, and uses external balancing circuits, if necessary, to null any remaining output offset voltage.

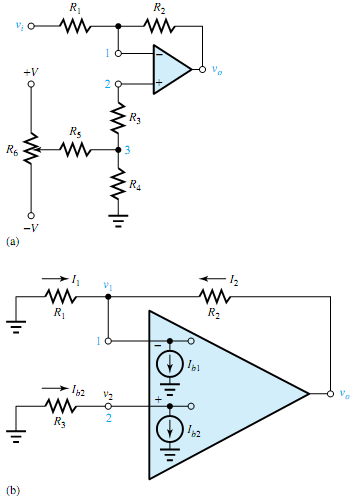

(a) Consider the input-offset voltage-nulling circuit for an inverting amplifier shown in Figure (a). Let R1 = 1.5k �,R2 = 22 k�, R6 = 100 k�, R5 = 500 k�, R4 = 200 �, and V = 12 V. Find the range of input offset voltages that can be generated at terminal 2 of the op amp. Also find R3 such that the input terminals see the same external resistance to ground.

(b) To examine the effects of input bias currents on the inverting amplifier, consider the circuit shown in Figure. Show that it is desirable to choose R3, which is equal to a parallel combination of R1 and R2. Compare the residual output voltage to what occurs if R3 were zero.

(c) Reconsider the circuit of part (b). Let R1 = 5k�, and R2 = 70 k�. Let the op-amp bias currents be Ib1 = 50 nA and Ib2 = 60 nA, but otherwise let the op amp be ideal. Determine the value of R3 that should be used.Also,when the input signal is zero, find the residual output offset voltage.