Give the circuit of a TTL NAND gate and explain its operation in brief.

Ans:

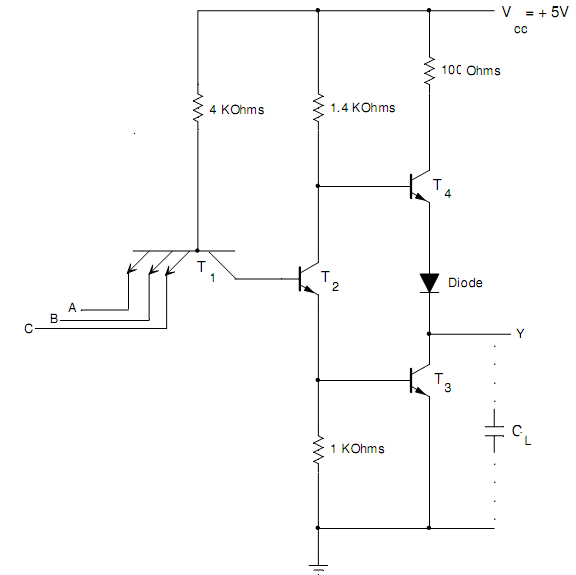

Operation of TTL NAND Gate: Fig.(d) Demonstrates a TTL NAND gate with a totem pole output. The totem pole output implies that transistor T4 sits atop T3 in order to give low output impedance. The low output impedance means a short time constant RC therefore the output can change rapidly from one state to the other. T1 is a multiple type emitter transistor. Such transistor can be thought of like a combination of various transistors along with a common collector and base. Multiple emitter transistors along with about 60 emitters have been developed. In this figure, T1 has 3 emitters thus there can be three inputs A, B, C. The transistor T2 functions as a phase splitter since the emitter voltage is out of phase along with the collector voltage. The transistors T3 and T4 by the totem pole output, the capacitance CL shows the stray capacitance and so on. The diode D is added to make sure that T4 is cut off while output is low. The voltage drop of diode D remains the base-emitter junction of T4 reverse biased therefore only T3 conducts while output is low. The operation can be described briefly by three conditions as specified below:

Condition 1: At least one input is low (that is, 0). Transistor T1 saturates. Thus, the base voltage of T2 is almost zero. T2 is cut off and forces T3 to cut off. T4 functions as an emitter follower and couples a high voltage to load. Output is high (that is Y=1).

Condition 2: Each input is high. The emitter base junctions of T1 are reverse biased. The collector base junction of T1 is forward biased. Therefore, T1 is in reverse active mode. The collector current of T1 flows in reverse direction. Because this current is flowing in the base of T2, the transistors T2 and T3 saturate and then output Y is low.

Condition 3: The circuit is operating under II while one of the inputs becomes low. The consequent emitter base junction of T1 starts conducting and T1 base voltage drops to a low value. Thus, T1 is in forward active mode. The high collector current of T1 shifts the stored charge in T2 and T3 and hence, T2 and T3 go to cut-off and T1 saturates and then output Y returns to high.

Fig.(d) Logic Diagram of TTL NAND Gate with Totem Pole Output