Explain the principles of operation of centralized SPC and distributed SPC and compare their performance.

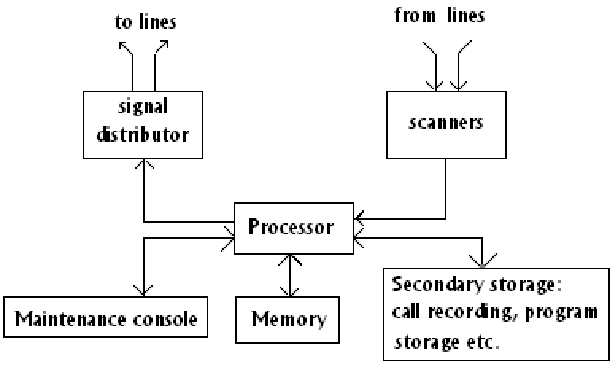

All the control equipment is replaced with a single processor that must be rather powerful, in centralized control. This must be able of processing 10 to 100 calls per second, depending upon the load on the system, and concurrently performing various ancillary tasks. A typical an ESS control configuration by using centralized SPC is demonstrated in figure. A centralized SPC configuration may utilize more than one processor for redundancy reasons; two approaches are there to organizing stored program control:

Centralized: In this type control, all the control equipment is replaced with a single processor that must be fairly powerful.

Distributed: In such controlling, the control functions are shared through many processors within the exchange itself.

Dual processor architecture may be configured in centralized SPC to operate in one of three modes which are given below:

Standby mode: In this, one processor is active and another is on standby, both software and hardware wise. This standby processor brought online while active processor fails. Significant requirement of this configuration is the capability of the standby processor to reconstitute the state of the exchange system, while this takes over the control.

Synchronous duplex mode: In this mode, hardware coupling is given between the two processors that execute similar set of instructions and compare the results continuously. When a mismatch arises, the faculty processor is specified and taken out of service instantly. If the system is operating generally, the two processors have similar data in their memories at all the time and receive all information from the exchange environment.

Load sharing mode: In this operation, an incoming call is allocated randomly or into a predetermined order to one of the processors that after this handles the call right by completion. Therefore both the processors are active concurrently and share the resources and the load dynamically.

FIG - Typically Centralized SPC Organization.