Reference no: EM131517499

Question 1. A CPU has 6 bits physical address and generates addresses 00,01, 02, 04 ,08 06 , 10, 0E, OF and 16 in hex.

A. Show the contents of the cache using two way set associative mapping, assume LRU replacement policy.

| |

V |

TagData |

B1 |

B0 |

LRU |

|

00

|

|

|

|

|

|

|

01

|

|

|

|

|

|

|

10

|

|

|

|

|

|

|

11

|

|

|

|

|

|

|

V

|

TagData

|

B1

|

B0

|

LRU

|

|

00

|

|

|

|

|

|

|

01

|

|

|

|

|

|

|

10

|

|

|

|

|

|

|

11

|

|

|

|

|

|

Question 2. Computer has 24 bits physical address and each memory location holds one byte. This computer has 64 cache lines ( 64 blocks), each block holds 16 bytes. Show format of address bus (tag , Index, and byte offset) using

A. Direct mapping.

B. 4 way set associative

C. 8 way set associative

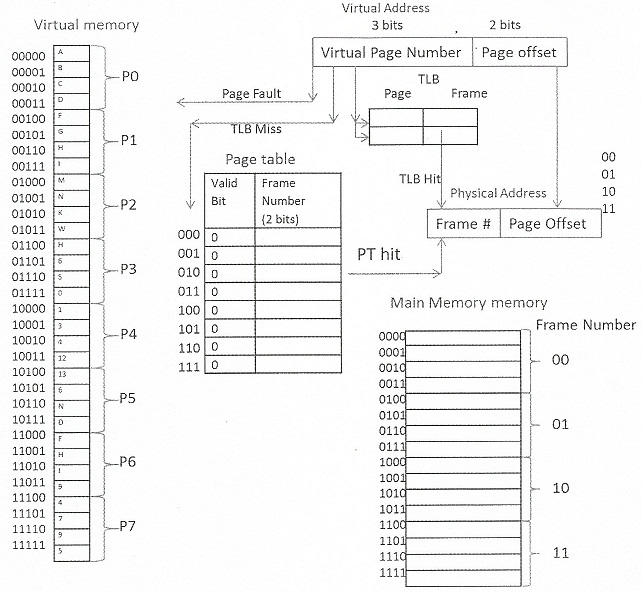

Question 3. A computer has 16Kbytes of virtual memory, 8 Kbytes of main memory and page size of IK bytes. Following figure shows TLB and page table of the computer.

1. How many bits is virtual address

2. How many pages are in virtual memory

3. How many bits require for physical address

4. How many frames (blocks) are in main memory

5. Following virtual addresses are given, find physical addresses and identify if each address generates TLB Hit page, Page table Hit or(page fault or not

|

Address TLB Hit Page Table Hit Page fault Physical address

3BAA hex

ICAChex

344F hex

|

Page Number Frame Number

TLB

Page table Page frame V

|

0000

|

110

|

1

|

|

0001

|

111

|

1

|

|

0010

|

101

|

1

|

|

0011

|

-

|

0

|

|

0100

|

001

|

1

|

|

0101

|

100

|

1

|

|

0110

|

|

0

|

|

0111

|

|

0

|

|

1000

|

- .

|

0

|

|

1001

|

|

0

|

|

1010

|

000

|

1

|

|

1011

|

-

|

0

|

|

1100

|

-

|

0

|

|

1101

|

|

0

|

|

1110

|

-

|

0

|

|

1111

|

-

|

0

|

Question 4. A processor has 32 bits virtual address, 20 bits physical address, Assume size of each page is 8k bytes.

A. What is size of Virtual memory?

B. How many pages are in virtual memory?

C. How many blocks in Physical memory?

D. What is the size of Page table (number of locations and size of each location)

Question 5. Following figure shows Virtual, Main and Cache memories of a computer. Assume following Mapping

Page 4 maps to frame #3

Page 5 maps to frame #1

CPU generates address 12, 13, 16, and 17 in hex

A. Show the content of Page table, and TLB

B. What is Physical address for each virtual address?

C. Show the content of main memory and cache

E. Determine number of page fault