Reference no: EM131101143

E15: Fundamentals of Digital Systems - Fall 2010 - EXAM 2 PRACTICE

1. Analyze this sequential logic circuit.

The circuit below takes as input two 4Hbit binary numbers X and Y, and a 1-bit input EN. It outputs an 8Hbit binary number P. Input to the circuit, but not depicted in the diagram, are a clock line and a reset line, which are both connected to the shift register and to all of the flip-flops. Complete the timing diagram below with traces for the values of A, S, and P (V has already been filled in for you). You can use the space to the right of the diagram for scratch work.

Convert X, Y and the final value of P to their decimal equivalents.

For any numbers X and Y, what would the final value of P be, in terms of X and Y? That is, what function does this circuit compute?

2. Implement a sequential logic circuit to transmit asynchronous 2-E-1 data.

Your circuit should have four inputs: a clock line, a reset line, a 2-bit message D, and a 1-bit input EN. It should have two 1-bit outputs R and Y. Operation for the circuit is specified as follows:

- After a reset, the circuit is in an idle state. The ready-for-data output R is set to 1, and the data output Y is also set to 1. The circuit will remain in the idle state as long as EN is set to zero on a positive clock edge.

- To begin transmitting, the circuit's message input D is set to the desired message, and EN is set to 1. At the next positive clock edge, the circuit leaves the idle state, R is set to 0 to indicate that the circuit is not ready for further input, and Y is set to 0 as a start bit. After the positive clock edge, changing the message input D should not affect whether the circuit correctly sends the message that was originally input.

- For the next 2 clock cycles, R is kept at 0 while Y cycles through the bits of the message that was originally input, from LSB to MSB.

- During the subsequent clock cycle, Y is set to the correct parity bit: 1 if the message contained an even number of 1's, and 0 otherwise. R is still held at 0.

- In the next clock cycle, the circuit returns to the idle state, resulting in setting the data output to 1, and the ready-for-data output to 1 as well.

Draw a logic diagram for your circuit, including any necessary gates and flip-flops. You may omit the clock and reset lines for clarity. Your circuit's outputs should directly depend only on the current state of the flip-flops in the circuit.

3. Latches instead of flip-flops.

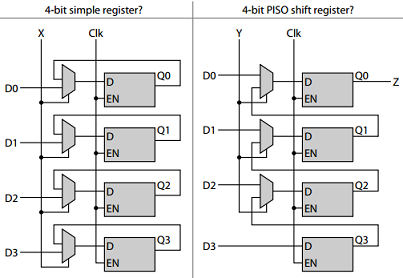

Fresh from his fiasco with the soda machine, Bob the digital circuit designer sets out to implement two register circuits: a 4-bit simple register, and a 4-bit PISO shift register. However, he has mistakenly built the circuits with D latches instead of D flip-flops, as in the diagrams below:

Note that the simple register is supposed to store D when X=1, and remain unchanged otherwise. The shift register is supposed to store D when Y=0 and shift to the right otherwise.

Assume that the inputs to the circuit are always set prior to the positive edge of the clock, and are always held until after the negative edge (i.e., the input never changes while the clock is held high). For each of the two circuits:

- Will the circuit work as intended, given the assumption above?

- If so, explain why. If not, draw a timing diagram leading to an incorrect output, and explain why the output is incorrect.

|

Can a homeless child including a undocumented homeless child

: Can a homeless child, including an undocumented homeless child, ever be required to show residency in a district in order to enroll in a district school?

|

|

Explore the legal rights and responsibilities of the tenant

: Describe whether or not Roger has a legal obligation to pay for the damage he caused and determine whether or not Larry would be liable for any direct damage.

|

|

Can we infer that differences exist between the four groups

: Can we infer that differences exist between the four groups?

|

|

Calculate the npv and the irr for each project

: calculate the NPV and the IRR for each project

|

|

Draw a logic diagram for your circuit

: E15: Fundamentals of Digital Systems - Fall 2010 - EXAM 2 PRACTICE. Draw a logic diagram for your circuit, including any necessary gates and flip-flops. You may omit the clock and reset lines for clarity. Your circuit's outputs should directly depe..

|

|

What issues zulima and joseph like to face in american court

: Shortly thereafter, Joseph arrives in America and successfully recuses his daughter. Zulima and her father then sue Salim in an American court for the return of the $420. What issues are Zulima and Joseph likely to face in an American court?

|

|

Calculate the irr, the npv, and the mirr for each project

: Edelman Engineering is considering including two pieces of equipment, a truck and an overhead pulley system, in this year's capital budget. The projects are independent. The cash outlay for the truck is $17,100, and that for the pulley system is $22,..

|

|

Operating at a negative to you still get taxed

: Interest 60000and tax rate 35%. What is net loss and what is operating cash flow.? So, I calculated EBIT - 155000, EBT - 215000 Here should taxes be 35% of EBT? Confused . If you are operating at a negative to you still get taxed?

|

|

Percent simple interest

: Gerold invested $118 in an account that pays 6 percent simple interest. How much money will he have at the end of 6 years?

|