Q. Define Wilkes Control Unit?

Prof. M. V. Wilkes of the Cambridge University Mathematical Laboratory invented the term microprogramming in 1951. He offered a systematic alternative process for designing control unit of a digital computer. At the time of instruction executing a machine instruction, a sequence of transformations and transfer of information from one register in processor to another take place. These were also known as the micro operations. Due to the analogy between the executions of individual steps in a machine instruction to execution of individual instruction in a program. Wilkes introduced the idea of microprogramming. Wilkes control unitreplaces the combinational and sequential circuits of hardwired CU by a simple CU in conjunction with a storage unit which stores the sequence of steps of instruction which is a micro-program.

In Wilkes microinstruction has two main components:

a) Control field thatdenotes the control lines which are to be activated and

b) Address field that provides address of the subsequent microinstruction to be executed.

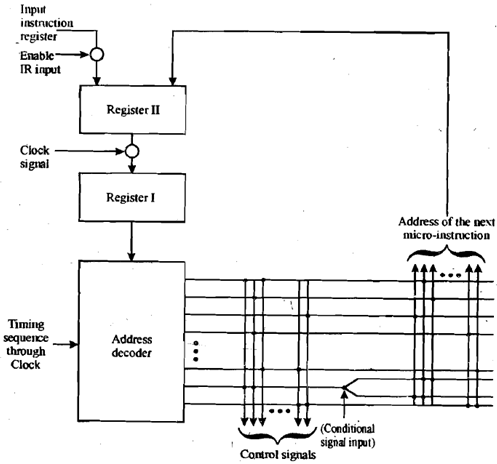

The figure below is an illustration of Wilkes control unit design.

Figure: Wilkes Control Unit

The control memory in Wilkes control is organized like a PLA's like matrix made of diodes. This is partial matrix and comprises two components the control signals and address of the subsequent micro-instruction. Register I comprises the address of next micro-instruction which is one step of instruction execution, for illustration T1 in M1 or T2 in M2 etc. as in Figure below. On decoding the control signals are producedwhich cause execution of micro-operation(s) of that step. Additionally the control unit denotes the address of next micro-operation that gets loaded through register II to register I. Register I can also be loaded by register II and enable IR input control signal. This will pass address of first micro-instruction of execute cycle. At the time of a machine cycle one row of the matrix is triggered. The first portion of the row produces the control signals which control the operations of the processor. Second part produces the address of row to be selected in next machine cycle.

At beginning of the cycle the address of the row to be selected is contained in register I. This address is input to decoder that is activated by a clock pulse.

This triggers the row of control matrix. Two-register arrangement is required as the decoder is a combinational circuit; with only one register output would become input at the time of a cycle. This can be an unstable condition because of repetitive loop.