Reference no: EM13841769

The objectives of this experiment are to:

1. Examine the operation of the RS latch.

2. Examine the operation of the D-type flip flop.

3. Examine the operation of the JK flip flop.

Introduction A flip flop is an essential building block of many important and useful circuits, such as counters, shift registers, and memories.

Basically, a flip flop stores a zero or a one. One or more inputs are provided to change the state of the flip flop. In this experiment we will examine the operation of several common flip flops.

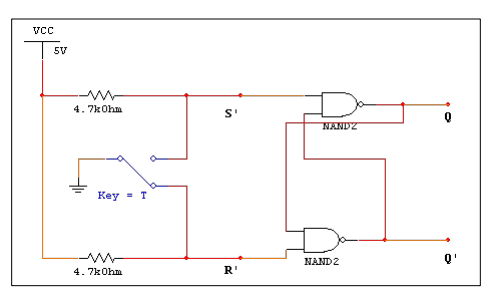

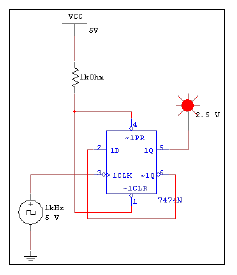

Procedure 1. Load the circuit E6A-1.MS7, shown in Figure 6A.1

Figure 6A.1: RS latch

Attach logic indicators and simulate the circuit. Which indicator is on?

2. Press ‘T' several times. What happens at the Q and Q' outputs?

3. In the real world, the SPDT switch suffers from mechanical contact bounce, which in turn generates hundreds or even thousands of edges before settling. The RS latch debounces the switch, providing one clean edge on its output for each toggling of the input. This edge can be used to provide a single clock pulse to a flip flop, counter, or shift register. MultiSim contains several built-in RS latches in the Miscellaneous Digital parts bin.

Figure 6A.2 shows one example.

Figure 6A.2: Built-in RS latch

Add the SPDT switch to the inputs with the proper pullups and verify that the built-in RS latch works the same as the circuit in Figure 6A.1.

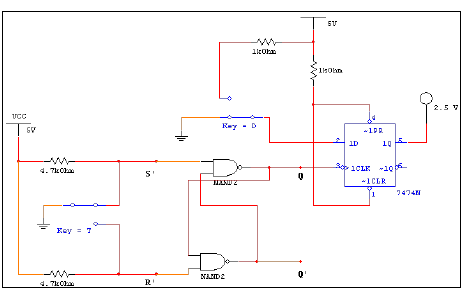

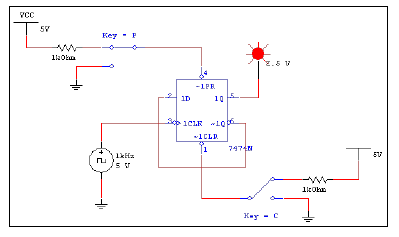

4. Load the circuit E6A-2.MS7, shown in Figure 6A.3, which uses the RS latch as the clockpulse circuit for a D-type flip flop. The data input to the flip flop is controlled by the D switch.

Figure 6A.3: Type-D flip flop

5. Determine what edge the D flip flop responds to (positive or negative).

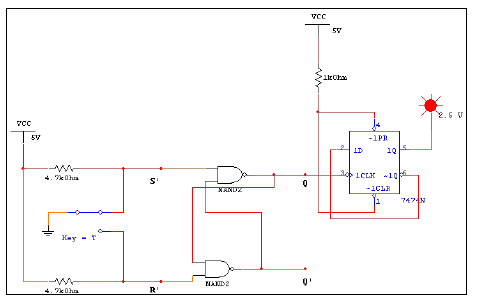

6. Load the circuit E6A-3.MS7, shown in Figure 6A.4. The D flip flop has its Q' output wired back to the D input. This enables a special mode called toggle, where the state of the output alternates between zero and one every two clock cycles. Verify this by pressing ‘T' ten times.

How many times does the logic indicator flash?

Figure 6A.4: D flip flop wired for toggle mode

7. Load the circuit E6A-4.MS7, shown in Figure 6A.5.

Figure 6A.5: Divide-by-two circuit

Verify (using the oscilloscope or logic analyzer) that the frequency of the waveform at the Q output is 500 Hz.

8. Add a second D flip flop (wired for toggle). The Q output of the first flip flop connects to the clock input of the second. What is the frequency at the second Q output?

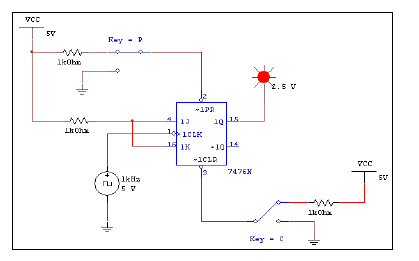

9. Load the circuit E6A-5.MS7, shown in Figure 6A.6. Now the asynchronous preset and clear inputs are used. The upper input (connected to the P switch) is the Preset input, which causes Q to go high, regardless of the clock state, whenever Preset is low. The lower input is the activelow Clear input, which forces Q low when active. Verify the operation of the Preset and Clear inputs by toggling ‘P' and ‘C' during simulation.

Figure 6A.6: D flip flop with asynchronous inputs

10. Load the circuit E6A-6.MS7, shown in Figure 6A.7.

Figure 6A.7: JK flip flop wired for toggle mode

11. With the J and K inputs tied high, the output of the JK flip flop will toggle to the opposite state upon each negative edge of the clock. Verify that the JK flip flop is negative-edge triggered.

12. Verify that the Preset and Clear inputs are active low (using ‘P' and ‘C').

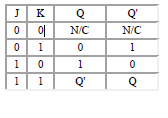

13. The truth table for the JK flip flop is shown in Table 6A.1. Verify the four modes of

operation.

Table 6A.1: Truth table for the JK flip flop

When J and K are both low, the outputs do not change state when the flip flop is clocked. When J is low and K is high, Q goes low after the next clock pulse. This mode is called clear. When J is high and K is low, Q is set after the next clock pulse. Toggle mode is selected when J and K are both high. "What is the difference between a synchronous input (D, J, or K) and an nchronousinput(PR or CLR)?"

Discussion

While reviewing your data and results, provide detailed answers to each of the following:

1. How does the built-in RS latch in the Miscellaneous Digital parts bin differ from the NAND gate circuit in E6A-1.MS7?

2. Do the type-D and JK flip flops respond to the same clock edge?

3. Explain how toggle mode is the same as division by two.

4. What is the difference between a synchronous input (D, J, or K) and

Attachment:- m5_multisim_lab.zip