Define the Gauss Seidel Method

The Gauss-Seidel method is an iterative method in which the voltage of each node is calculated in turn using the most up to date voltages for the other nodes. The voltage calculated is that which gives the correct solution for the node considered, based upon the data specified and the previously calculated voltages of the other nodes. The method is equally applicable to both a.c. and d.c. circuits.

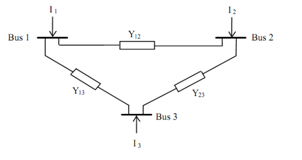

Consider the three busbar system shown in Figure.

Using Nodal analysis, the current fed into each bus is given as:

I1 = Y11 V1 + Y12 V2 + Y13 V3

I2 = Y21 V1 + Y22 V2 + Y23 V3

I3 = Y31 V1 + Y32 V2 + Y33 V3

or, in matrix form,

[I] = [Y] [V]

where Ynn is node n self admittance (sum of all the admittances connected to node n).

Ynm is the mutual admittance between nodes n and m (sum of the admittances connecting node n to node m)

Note that: (i) all mutual admittance terms have a negative sign,

(ii) all injected currents are positive.

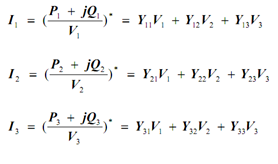

Recalling that S = P + j Q = V I *

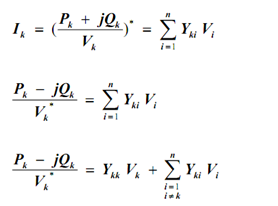

In general, for an n busbar system, the current fed into busbar k is given as:

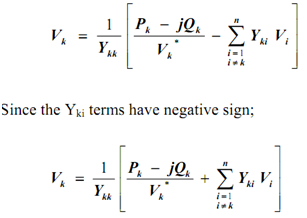

Therefore, the voltage at busbar k is given as:

Where Vk and Vi are the voltages at nodes 'k' and 'i', respectively,

Ykk is node 'k' self admittance,

Yki is the mutual admittance between nodes 'k' and 'i',

Pk - jQk is the total power flowing into node 'k'.