Reference no: EM131433566

Lab Assignment

The objective of this lab is to practice your Verilog coding and the design of a Finite State Machine.

Lab Goal:

For this lab, you will code a Verilog module to implement the FSM described in this document. This lab will also require that you use the Seven-Segment Display on the DE0-CV FPGA board.

Design Specifications for the FSM

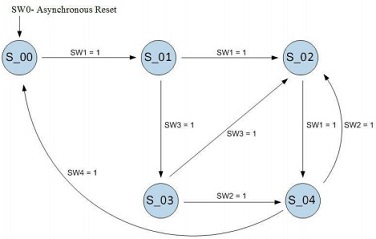

Implement the following simple state machine on the DE0-CV FPGA board. This FSM will have 5 states. The clock to this FSM will be provided by yourself using KEY0 (one of the push buttons on the board). It is highly recommended that you use a debounce module (to be covered in class) to ensure that spurious clocks do not occur when using a push-button to emulate a clock.

The transitions from any one state to another are determined by switches 0 through 4 of the board (SW0, SW1, SW2, SW3, and SW4) as shown in the state diagram below. This will be easier than using pushbuttons for the inputs to switch to states. That means you set the switch and then clock using KEY0. It really only matters what the switches are doing when the clocking occurs.

NOTE reiterating this use Switches instead of pushbuttons for input. Use KEY0 for clock.

Any input transition not explicitly referenced in the diagram keeps the machine in the same state. Moreover, if two or more switches are asserted simultaneously, no transition should occur. In other words, the switches are to be treated as one-hot and your design should enforce this provision. The only exception to this is SW0 which acts as the reset and should reset the FSM to S_00 regardless of all other switches or the pushbutton. (note you could use KEY1 pushbutton instead but it isn't clear that would be better).

Required use of the 4-digit, 7-segment display

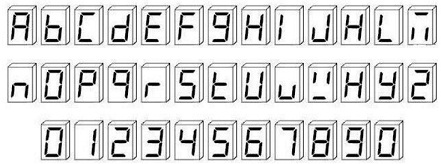

The 7-segment display should be used to indicate which state the FSM is in. For S_01, S_02, S_03, and S_04 the 4-digit display should display exactly that: S_01, S_02, S_03, or S_04. The one exception is that whenever the machine is in S_00, the 4-digit, 7-segment display should display the first four digits of your last name using the table below.

There is an onboard oscillator (50 MHz). Do not use the clock to clock the FSM, use KEY0, the FSM cannot work from the internal clock because you have to change input between clocks. Pin configurations can be found in section 3.4 of the DE0-CV manual. For information on how to use 7-segment display, refer to the section 3.3 in the manual.

Required use of LEDs

Whenever any of the switches (SW0, SW1, SW2, SW3, and SW4) are in the ON position, the corresponding LED (LEDR0, LEDR1, LEDR2, LEDR3, and LEDR4) should be ON.

Submission of Completed Lab:

Please upload the following files to the Lab3 Submission link on Blackboard:

• All Verilog source files (including testbech, and submodules)

• Board programming file (lab3.sof file which can be found in output files directory)

• A lab report in PDF format, include following in the report:

o Waveform simulations covering all transitions and proving the full functionality.

o Brief explanations of the design and organization of your code (Code snippets can be helpful in your explanations)

o Brief explanation of the tests you performed in your testbench

• You can use the following test sequence: SW0 - 10000000000000000

SW1 - 00111010010101000

SW2 - 00000000001000010

SW3 - 00000001100000100

SW4 - 00000100000010001.

|

Which of his books are considered to be best

: Patrick Lencioni is a founder of which company? Which of his books are considered to be best?

|

|

What is meant by a frame structure

: What is meant by a frame structure and state the two classifications of frames

|

|

Effective project risk management factors and techniques

: For your risk management assignment, do some of your own research into effective project risk management factors and techniques. Develop a working excel model that puts weights on your selected factors and produces a score that can show what the degr..

|

|

English-only rule create lower morale

: 1. In a workplace with a diverse workforce, how could an English-only rule create lower morale, poorer communication, and lower productivity. Explain and provide example(s).

|

|

Design specifications for the finite state machine.

: Design Specifications for the Finite State Machine. You will code a Verilog module to implement the FSM described in this document. This lab will also require that you use the Seven-Segment Display on the DE0-CV FPGA board.

|

|

Explain part of the vba program

: PAris timezone and the format should be a access database like the one I have sent you. I need the writer to explain part of the VBA program. Tell me if you can do it

|

|

Compute the probability of the top event

: a. What equation should you use to compute the probability of the top event? b. Using the equation, what numerical value do you get for the top event probability? c. For the top event, what is the probability of the complimentary event (i.e., success..

|

|

Competitive forces in porters model for industry analysis

: Which of the following is one of the primary competitive forces in Porter's model for industry analysis? The strategic-management process requires. The lower the barriers to entry in an industry, the more attractive that industry is.

|

|

What is change management

: Select the Write New Message icon to answer the following questions. Make sure you integrate concepts from the course materials, including , with your answer.Include all of your answers in a single post of 150-300 words. Your answers should contai..

|