SISO Shift Register:

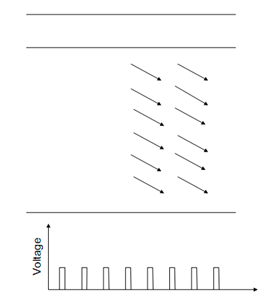

A SISO shift register is illustrated in Figure. Here the data are serially entered one by one through the input terminal D1 and serially taken out through Q3. Whereas the first clock pulse is applied, data from D1 will go to Q1, D2 shall go to Q2 and D3 shall go to Q3. For each clock pulse, the data shall get shifted through the Flip Flops in progression and they may be read from the output Q3 serially in synchronism with the system clock pulse. For instance when a data 01101 is entered through D1, the shifting of bit information for each of the clock pulse is given in Figure. Note down that the first data to be entered for SISO Shift Register is MSB and for this case is 0. Then in the next clock pulse the next MSB, that means. 1 is entered to D1 and so on.

Figure: Shift Table for 3 Element SISO Shift Register