Merits and Demerits of Voltage divider bias:

Merits:

1. Not like the above circuits, only one dc supply is essential.

2. Operating point is approximately independent of β variation.

3. Operating point stabilized against shift in temperature.

Demerits:

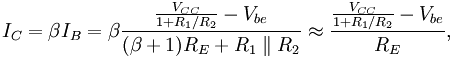

In this circuit, to keep IC independent of β the following condition must be met:

That is approximately the case if

(β + 1) RE >> R1 || R2

In which R1 || R2 represents the equivalent resistance of R1 and R2 connected in parallel.

As β-value is set for a given transistor, this relation can be fulfilled either by keeping RE fairly large, or making R1||R2 extremely low.

If RE is of large value, high VCC is essential. This get increases cost as well as precautions essential while handling.

Either R1 is low, or R2 is low, or both are low if R1 || R2 is low. A low R1 raises VB closer to VC, get reducing the available swing in collector voltage, and limiting how large RC can be made with no driving the transistor out of active mode. A low R2 lowers Vbe, reducing the permitted collector current. Lowering both of the resistor values draws much more current from the power supply and lowers the input resistance of the amplifier as observed from the base.